Описание

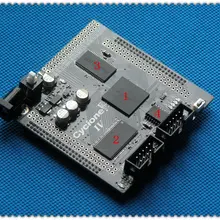

Этот продукт может быть применен для высокой скорости, больших данных, плотной работы и других встроенных проектов. Все, что вам нужно сделать, это сделать довольно простой пол для него. Реальное "минимальное ядро"!

Цель заключается в использовании дополнительной аппаратной системы для выполнения некоторых дорогих работ для других сопроцессоров, таких как MCU, ARM и DSP, и вывода только на сопроцессор.

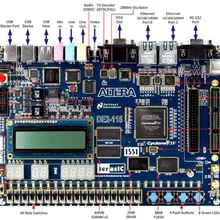

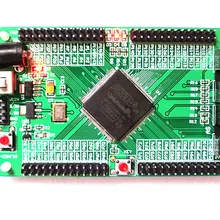

Базовая конфигурация основной платы:

Наименование Описание серийного номера

1 FPGA основной чип EP4CE55F23 (55856 LE, 2396 K бит ram, 312 мультипликатор, 4 PLLs)

2 FPGA чип конфигурации WINBOND W25Q64 (64 Мбит)

Плата 3 загружена SDRAM двумя частями MT48LC8M32B2 (8 м * 32 бит) (512 Мбит), и адресная шина данных полностью независима

4 доска загружены SRAM

ISSI 25616, 256 K * 16 бит

5 тактовый 27 МГц, 50 МГц активный кварцевый генератор

6 Чип шифрования DS28E01, Защитите ваш дизайн от кражи

7 интерфейс питания + 3 V ~ + 15 V DC вход питания, + 3,3 V 2A выход

8 внешних расширителей интерфейса GIOP0 (41 IO), GPIO1 (45 IO), FPC (22 IO) общее внешнее расширение 108 IO, расстояние 1,27 мм

Размер 9 основной пластины 40 мм x 40 мм, а установочное отверстие 38 мм x 38 мм

Эксперимент и его Код:

Программное обеспечение 1. SDCARD-SPI (FAT & amp; FAT32) распакует изображение JPG и отображает эксперимент через изображение вывода VGA (максимальная поддержка 1920*1080 @ 60 Гц).

2. SDCARD-SPI (FAT & amp; FAT32) аппаратная декомпрессия MP3 файла (внимание MP3 не WAV) и воспроизведение, звуковой сигнал в режиме реального времени FFT преобразования, через VGA для отображения спектра.

3. На аудио сигнал сбора и в режиме реального времени FFT преобразования, с помощью VGA для отображения спектра.

40 миллионов пикселей уровень цифровой камеры эксперимент. Мы собираем данные изображения CMOS датчика изображения и имеем SDCARD на BMP или формате JPG (максимальная поддержка 1600 Вт пикселей).

В эксперименте 5. IPCAMERA изображения, собранные cmos-датчиком изображения, передаются на верхний компьютер через сеть.

6., фронтальная обработка визуального изображения, фильтрация изображения в реальном времени, обнаружение краев, молотилка, выравнивание гистограммы, обнаружение движения и так далее сделаны для изображения, собранного CMOS датчиком изображения.

Следующая схема-интерфейс основной платы. GPIO0 является общим 3,3 V IO, который приводит к сигналу JTAG.

Часть GPIO1 может использоваться как общий IO для 3,3 В или 2,5 в, или использоваться в качестве LVDS;

Интерфейс FPC 3.3VIO, который может быть напрямую подключен к другим модулям CMOS в магазине.

Характеристики

- Бренд

- BETTERSHENGSUN

- Индивидуальное изготовление

- Да

- Test1

- 4

- Номер модели

- EP4CE55F23

- Test4

- 4