Описание

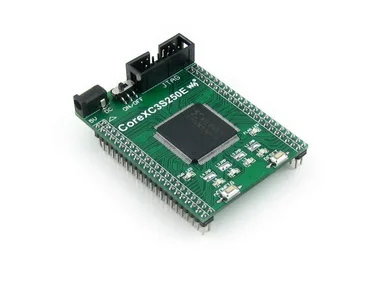

XILINX FPGA Совет развития Core Xilinx Spartan-3E XC3S250E оценочная плата + XCF02S флэш-в JTAG = Core3S250E

Процессор FPGA core, оснащен чипом XILINX Spartan-3E XC3S250E бортовой

Обзор

Core3s250e является процессором FPGA, который имеет XC3S250E устройство на борту, поддерживает дальнейшее расширение.

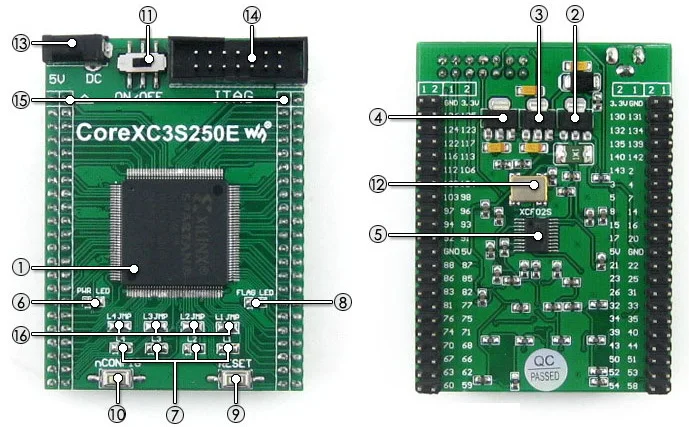

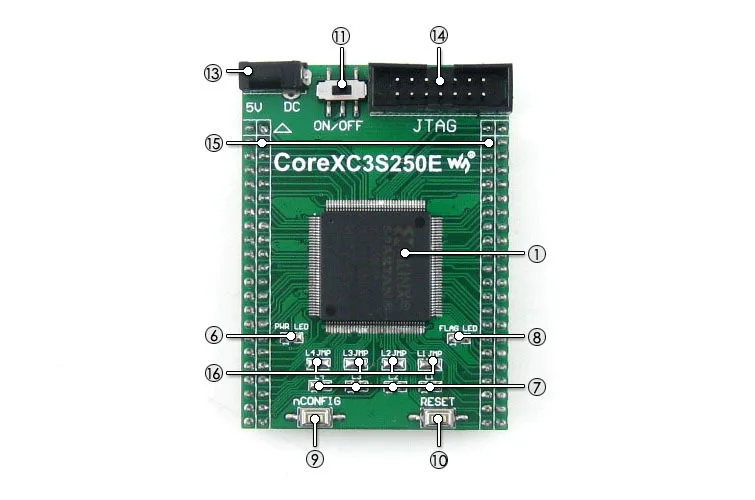

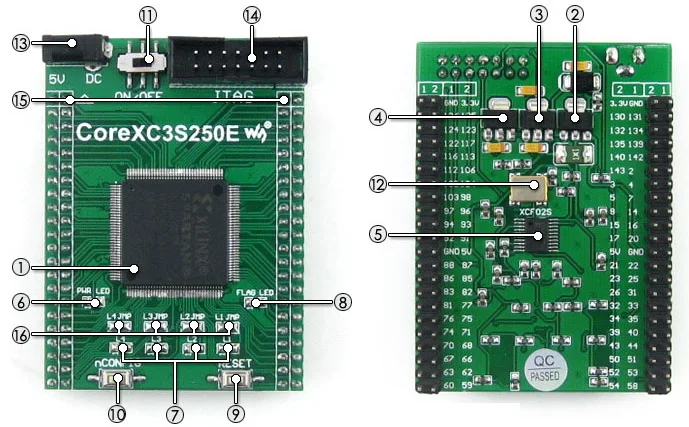

На борту 1 шт. XCF02S Интегрированный базовый канал FPGA, такой как контура часов Бортовой Кнопка nCONFIG, кнопка сброса, 4 x светодиоды Все порты I/O доступны на штырьковых заголовках Встроенный интерфейс JTAG отладки/программирования Конструкция головки 2,54 мм, пригодная для подключения к сети, в системе приложенияЧто на борту

XC3S250E:Устройство XILINX Spartan-3E FPGA, которое имеет: Рабочая частота:50 мГц Рабочая Напряжение:1,15 В~3,3 В Посылка:QFP144 Я/Os:80 LEs:250 К Оперативная память:216kb DCMs:4 Отладка/программирование:Поддерживает JTAG AMS1117-3.3,3,3 В регулятор напряжения AMS1117-2.5,2,5 В регулятор напряжения AMS1117-1.2,1,2 В регулятор напряжения XCF02S,Бортовой флэш-память для хранения кода Мощность индикатор Светодиоды FPGA инициализации индикатор Кнопка сброса Кнопки nCONFIG:Для повторной настройки микросхемы FPGA, эквивалентной пересетке питания Мощность переключатель 50 м активный кристалл осциллятор 5 В DC jack Интерфейс JTAG:Для отладки/программирования FPGA булавки расширитель,VCC, GND и все порты I/O доступны для расширения разъемов для дальнейшего расширения Светодиодный джемперы

XC3S250E:Устройство XILINX Spartan-3E FPGA, которое имеет: Рабочая частота:50 мГц Рабочая Напряжение:1,15 В~3,3 В Посылка:QFP144 Я/Os:80 LEs:250 К Оперативная память:216kb DCMs:4 Отладка/программирование:Поддерживает JTAG AMS1117-3.3,3,3 В регулятор напряжения AMS1117-2.5,2,5 В регулятор напряжения AMS1117-1.2,1,2 В регулятор напряжения XCF02S,Бортовой флэш-память для хранения кода Мощность индикатор Светодиоды FPGA инициализации индикатор Кнопка сброса Кнопки nCONFIG:Для повторной настройки микросхемы FPGA, эквивалентной пересетке питания Мощность переключатель 50 м активный кристалл осциллятор 5 В DC jack Интерфейс JTAG:Для отладки/программирования FPGA булавки расширитель,VCC, GND и все порты I/O доступны для расширения разъемов для дальнейшего расширения Светодиодный джемперыФотографии

Примечание:

Core3s250e предоставляет интерфейс отладки JTAG, пока не интегрирует какую-либо функцию отладки, отладчик требуется.

Мамин плата и программист/отладчик на фото не включены в цену.

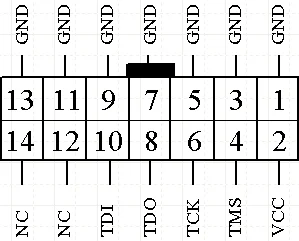

Отладка/программирование Интерфейс

Основная плата core3s250e FPGA интегрирует интерфейс JTAG для программирования/отладки.

Имена и описание сигнала JTAG

| Pin | Имя сигнала | Описание |

|---|---|---|

| 1 | GND | Сигнальной земли |

| 2 | VCC (TRGT) | Цель источника питания |

| 3 | GND | Сигнальной земли |

| 4 | TMS | JTAG Состояние управления машиной |

| 5 | GND | Сигнальной земли |

| 6 | ТСК | Тактового Сигнала |

| 7 | GND | Сигнальной земли |

| 8 | TDO | Данные от устройства |

| 9 | GND | Сигнальной земли |

| 10 | TDI | Данные устройства |

| 11 | GND | Сигнальной земли |

| 12 | NC | |

| 13 | GND | Сигнальной земли |

| 14 | NC | |

| 15 | GND | Сигнальной земли |

Заголовок JTAG распиновка

Ресурсов развития

Core3s250e fpfpga основная плата поставляется с пользователем пользователя CD, включая ресурсы развития, перечисленные ниже:

Связанное программное обеспечение (Xilinx ISE 12-Поддерживает Winxp/Win7, не поддерживает Win8) ДЕМО код (Verilog, VHDL) Схема (PDF) FPGA документация развитияПосылка содержит

Core3S250E основной плате х 1 USB кабель питания x 1

1

2

Покупатели, которые купили этот товар, также купили

Характеристики

- Номер модели

- Core3S250E

- Тип демоплаты

- Рука

- Бренд

- Waveshare

- Package

- QFP144

- Operating Voltage

- 1.15V~3.3V

- supports JTAG

- 50MHz

- Debugging/Programming

- supports JTAG

- header pitch design

- 2.54mm

- JTAG debugging/programming interface

- Yes, onboard

- all the I/O ports

- are accessible on the pin headers

- integrated FPGA basic circuit

- are accessible on the pin headers

- Core3S250E

- an FPGA core board

- Model Name

- Core3S250E

- Demo Board Type

- Others